아날로그 회로 설계 질문입니다.

페이지 정보

capstone 작성일2017-05-29 01:29관련링크

본문

안녕하세요. 전자공학과 4학년 학부생입니다.

이번에 아날로그 설계과목을 듣는데, 설계 과제 도중 도저히 문제가 무엇인지 모르겠어서 질문 올립니다.

이번에 저전력 회로설계를 하게 되었는데요, 시뮬레이션을 돌리기 위해 HSPICE를 사용하는데, 다음과 같이 코드를 작성했습니다.(*모델도 첨부했습니다.)

LOWPOWER

** SPICE MODEL **

--------------------------------------------------------------

.MODEL CMOSN NMOS( LEVEL=49

+VERSION=3.1 TNOM=27 TOX=1.39E-8

+XJ=1.5E-7 NCH=1.7E17 VH0=0.719346

+K1=0.9504347 K2=-0.1223091 K3=32.8194652

+K3B=-18.2798187 W0=6.962875E-7 NLX=1E-9

+DVT0W=0 DVT1W=0 DVT2W=0

+DVT0=2.8679381 DVT1=0.364583

+DVT2=-0.1457773

+U0=457.9817288 UA=1.760644E-11

+UB=6.60249E-19

+UC=-2.21616E-11 VSAT=2E5 A0=0.2569008

+AGS=0 B0=2.419162E-6 B1=2.998423E-6

+KETA=-0.0151838 A1=2.11776E-5 A2=0.3164018

+RDSW=1.7986E3 PRWG=7.186697E-3

+PRWB=0.0286192

+WR=1 WINT=2.280272E-7 LINT=4.223411E-8

+XL=0 XW=0 DWG=-1.412924E-8

+DWB=2.266359E-8 VOFF=-0.0138159

+NFACTOR=0.9403671

+CIT=0 CDSC=2.4E-4 CDSCD=0

+CDSCB=0 ETA0=0.038987

+ETAB=-4.142228E-3

+DSUB=0.2739841 PCLM=1.5957826

+PDIBLC1=-0.7948288

+PDIBLC2=2.031474E-3 PDIBLCB=-0.0280342

+DROUT=0.5770863

+PSCBE1=5.515654E8 PSCBE2=3.428003E-5

+PVAG=4.075335E-3

+DELTA=0.01 RSH=85.5 MOBMOD=1

+PRT=174.3465431 UTE=-1

+KT1=-0.3236204

+KT1L=-0.709202E-10 KT2=0

+UA1=1.768937E-9

+UB1=-4.48827E-18 UC1=-5.6E-11

+AT=8.009938E4

+WL=0 WLN=1 WW=0

+WWN=1 WWL=-6.554E-20 LL=0

+LLN=1 LW=0 LWN=1

+LWL=-9.461E-20 CAPMOD=2 XPART=0.4

+CGDO=2.04E-10 CGSO=2.04E-10 CGBO=1E-9

+CJ=4.225482E-4 PB=0.9767537 MJ=0.438383

+CJSW=3.727516E-10 PBSW=0.1

+MJSW=0.1242771

+CF=0 PVTH0=0.1503709 PRDSW=294.4686286

+PK2=0.0257664 WKETA=4.349461E-3

+LKETA=-3.275389E-3

+PVSAT=4.053601E4 )

.MODEL CMOSP PMOS( LEVEL=49

+VERSION=3.1 TNOM=27 TOX=1.39E-8

+XJ=1.5E-7 NCH=1.7E17 VH0=-0.9725622

+K1=0.0.5594978 K2=4.242915E-3 K3=0

+K3B=-2.1787058 W0=5.024966E-7 NLX=1E-9

+DVT0W=0 DVT1W=0 DVT2W=0

+DVT0=2.1983824 DVT1=0.4590354 DVT2=-0.0877166

+U0=230.1006352 UA=3.082914E-9

+UB=1E-21

+UC=-8.49253E-11 VSAT=1.799169E5 A0=0.9968666

+AGS=0.1886708 B0=1.56806E-6 B1=5E-6

+KETA=-4.636636E-3 A1=1.051164E-4 A2=0.4948895

+RDSW=1.934022E3 PRWG=0.0387677

+PRWB=-0.0761681

+WR=1 WINT=2.519308E-7 LINT=3.903552E-8

+XL=0 XW=0 DWG=-2.506572E-8

+DWB=9.639272E-9 VOFF=-0.0865101

+NFACTOR=0.6651504

+CIT=0 CDSC=2.4E-4 CDSCD=0

+CDSCB=0 ETA0=8.3524E-3

+ETAB=-1.59539E-3

+DSUB=0.1864431 PCLM=2.4907335

+PDIBLC1=0.4762146

+PDIBLC2=2.561625E-3 PDIBLCB=-0.1

+DROUT=0.7045912

+PSCBE1=1.484087E10 PSCBE2=1.453333E-9

+PVAG=2.5889735

+DELTA=0.01 RSH=102.5 MOBMOD=1

+PRT=22.2970225 UTE=-1

+KT1=-0.4690262

+KT1L=1.73235E-9 KT2=0

+UA1=1.953646E-9

+UB1=-7.64921E-18 UC1=-5.6E-11

+AT=-1E5

+WL=0 WLN=1 WW=0

+WWN=1 WWL=-1.205E-20 LL=0

+LLN=1 LW=0 LWN=1

+LWL=6.268E-21 CAPMOD=2 XPART=0.4

+CGDO=2.04E-10 CGSO=2.04E-10 CGBO=1E-9

+CJ=7.281027E-4 PB=0.9583121 MJ=0.4969115

+CJSW=2.724206E-10 PBSW=0.99

+MJSW=0.3063901

+CF=0 PVTH0=-0.0449356 PRDSW=0

+PK2=-1.037068E-3 WKETA=-9.521313E-3

+LKETA=7.063491E-4

)

--------------------------------------------------------------

** Netlist **

VDD 9 7 3V

Is1 8 7 100uA

M1 4 1 3 3 CMOSP W=37.5U L=1.5U

M2 5 2 3 3 CMOSP W=37.5U L=1.5U

M3 4 4 7 7 CMOSN W=15U L=1.5U

M4 5 4 7 7 CMOSN W=15U L=1.5U

M5 3 8 9 9 CMOSP W=75U L=1.5U

M6 6 5 7 7 CMOSN W=30U L=1.5U

M7 6 8 9 9 CMOSP W=75U L=1.5U

M8 8 8 9 9 CMOSP W=75U L=1.5U

C1 5 6 1p

V1 1 0 SIN(0.8V -1M 0.8k)

V2 2 0 SIN(0.8V 1M 0.8k)

** Simulation **

.temp 25

.tran 0.1m 10m

.op

.probe I(M1) I(M2) I(M3) I(M4) I(M5) I(M6) I(M7) I(M8)

.end

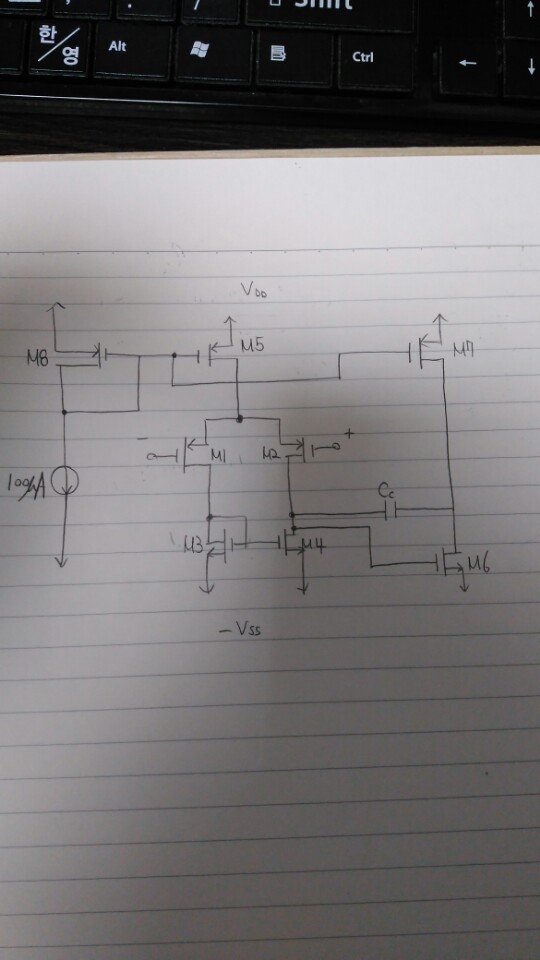

각 fet의 크기는 netlist에 적혀있고, 회로는 직접 사진찍어 첨부합니다.

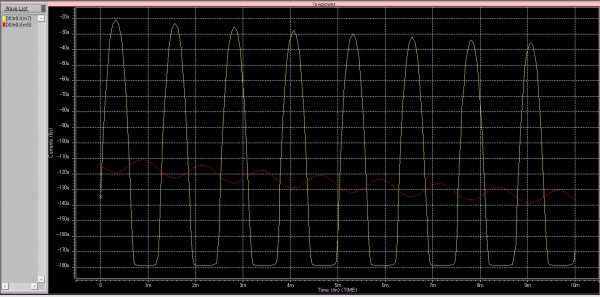

Q1) 이대로 시뮬레이션을 돌리면, M5와 M7의 드레인 전류가 요동칩니다. (사진 첨부했습니다.)

Q2) 이 드레인 전류가 불안정해서인지, 증폭 역시 잘 안되는데, 이게 드레인 전류 불안정 ,즉 모든

FET들이 saturation mode 에서 작동하지 않아서 output node에서 출력 swing이 이상한 것인지... 궁금합니다.

Q3) 그렇다면 이 문제들을 어떻게 해결해야할까요??

Q4) 소자 모델은 저것을 쓰는 것이 적합한 것인가요? ( neural opamp 설계 논문을 참조해서 쓴 모델인데, 더 적합한 모델 있다면 말씀해주시면 파라미터들은 찾아보겠습니다...)

이번에 아날로그 설계과목을 듣는데, 설계 과제 도중 도저히 문제가 무엇인지 모르겠어서 질문 올립니다.

이번에 저전력 회로설계를 하게 되었는데요, 시뮬레이션을 돌리기 위해 HSPICE를 사용하는데, 다음과 같이 코드를 작성했습니다.(*모델도 첨부했습니다.)

LOWPOWER

** SPICE MODEL **

--------------------------------------------------------------

.MODEL CMOSN NMOS( LEVEL=49

+VERSION=3.1 TNOM=27 TOX=1.39E-8

+XJ=1.5E-7 NCH=1.7E17 VH0=0.719346

+K1=0.9504347 K2=-0.1223091 K3=32.8194652

+K3B=-18.2798187 W0=6.962875E-7 NLX=1E-9

+DVT0W=0 DVT1W=0 DVT2W=0

+DVT0=2.8679381 DVT1=0.364583

+DVT2=-0.1457773

+U0=457.9817288 UA=1.760644E-11

+UB=6.60249E-19

+UC=-2.21616E-11 VSAT=2E5 A0=0.2569008

+AGS=0 B0=2.419162E-6 B1=2.998423E-6

+KETA=-0.0151838 A1=2.11776E-5 A2=0.3164018

+RDSW=1.7986E3 PRWG=7.186697E-3

+PRWB=0.0286192

+WR=1 WINT=2.280272E-7 LINT=4.223411E-8

+XL=0 XW=0 DWG=-1.412924E-8

+DWB=2.266359E-8 VOFF=-0.0138159

+NFACTOR=0.9403671

+CIT=0 CDSC=2.4E-4 CDSCD=0

+CDSCB=0 ETA0=0.038987

+ETAB=-4.142228E-3

+DSUB=0.2739841 PCLM=1.5957826

+PDIBLC1=-0.7948288

+PDIBLC2=2.031474E-3 PDIBLCB=-0.0280342

+DROUT=0.5770863

+PSCBE1=5.515654E8 PSCBE2=3.428003E-5

+PVAG=4.075335E-3

+DELTA=0.01 RSH=85.5 MOBMOD=1

+PRT=174.3465431 UTE=-1

+KT1=-0.3236204

+KT1L=-0.709202E-10 KT2=0

+UA1=1.768937E-9

+UB1=-4.48827E-18 UC1=-5.6E-11

+AT=8.009938E4

+WL=0 WLN=1 WW=0

+WWN=1 WWL=-6.554E-20 LL=0

+LLN=1 LW=0 LWN=1

+LWL=-9.461E-20 CAPMOD=2 XPART=0.4

+CGDO=2.04E-10 CGSO=2.04E-10 CGBO=1E-9

+CJ=4.225482E-4 PB=0.9767537 MJ=0.438383

+CJSW=3.727516E-10 PBSW=0.1

+MJSW=0.1242771

+CF=0 PVTH0=0.1503709 PRDSW=294.4686286

+PK2=0.0257664 WKETA=4.349461E-3

+LKETA=-3.275389E-3

+PVSAT=4.053601E4 )

.MODEL CMOSP PMOS( LEVEL=49

+VERSION=3.1 TNOM=27 TOX=1.39E-8

+XJ=1.5E-7 NCH=1.7E17 VH0=-0.9725622

+K1=0.0.5594978 K2=4.242915E-3 K3=0

+K3B=-2.1787058 W0=5.024966E-7 NLX=1E-9

+DVT0W=0 DVT1W=0 DVT2W=0

+DVT0=2.1983824 DVT1=0.4590354 DVT2=-0.0877166

+U0=230.1006352 UA=3.082914E-9

+UB=1E-21

+UC=-8.49253E-11 VSAT=1.799169E5 A0=0.9968666

+AGS=0.1886708 B0=1.56806E-6 B1=5E-6

+KETA=-4.636636E-3 A1=1.051164E-4 A2=0.4948895

+RDSW=1.934022E3 PRWG=0.0387677

+PRWB=-0.0761681

+WR=1 WINT=2.519308E-7 LINT=3.903552E-8

+XL=0 XW=0 DWG=-2.506572E-8

+DWB=9.639272E-9 VOFF=-0.0865101

+NFACTOR=0.6651504

+CIT=0 CDSC=2.4E-4 CDSCD=0

+CDSCB=0 ETA0=8.3524E-3

+ETAB=-1.59539E-3

+DSUB=0.1864431 PCLM=2.4907335

+PDIBLC1=0.4762146

+PDIBLC2=2.561625E-3 PDIBLCB=-0.1

+DROUT=0.7045912

+PSCBE1=1.484087E10 PSCBE2=1.453333E-9

+PVAG=2.5889735

+DELTA=0.01 RSH=102.5 MOBMOD=1

+PRT=22.2970225 UTE=-1

+KT1=-0.4690262

+KT1L=1.73235E-9 KT2=0

+UA1=1.953646E-9

+UB1=-7.64921E-18 UC1=-5.6E-11

+AT=-1E5

+WL=0 WLN=1 WW=0

+WWN=1 WWL=-1.205E-20 LL=0

+LLN=1 LW=0 LWN=1

+LWL=6.268E-21 CAPMOD=2 XPART=0.4

+CGDO=2.04E-10 CGSO=2.04E-10 CGBO=1E-9

+CJ=7.281027E-4 PB=0.9583121 MJ=0.4969115

+CJSW=2.724206E-10 PBSW=0.99

+MJSW=0.3063901

+CF=0 PVTH0=-0.0449356 PRDSW=0

+PK2=-1.037068E-3 WKETA=-9.521313E-3

+LKETA=7.063491E-4

)

--------------------------------------------------------------

** Netlist **

VDD 9 7 3V

Is1 8 7 100uA

M1 4 1 3 3 CMOSP W=37.5U L=1.5U

M2 5 2 3 3 CMOSP W=37.5U L=1.5U

M3 4 4 7 7 CMOSN W=15U L=1.5U

M4 5 4 7 7 CMOSN W=15U L=1.5U

M5 3 8 9 9 CMOSP W=75U L=1.5U

M6 6 5 7 7 CMOSN W=30U L=1.5U

M7 6 8 9 9 CMOSP W=75U L=1.5U

M8 8 8 9 9 CMOSP W=75U L=1.5U

C1 5 6 1p

V1 1 0 SIN(0.8V -1M 0.8k)

V2 2 0 SIN(0.8V 1M 0.8k)

** Simulation **

.temp 25

.tran 0.1m 10m

.op

.probe I(M1) I(M2) I(M3) I(M4) I(M5) I(M6) I(M7) I(M8)

.end

각 fet의 크기는 netlist에 적혀있고, 회로는 직접 사진찍어 첨부합니다.

Q1) 이대로 시뮬레이션을 돌리면, M5와 M7의 드레인 전류가 요동칩니다. (사진 첨부했습니다.)

Q2) 이 드레인 전류가 불안정해서인지, 증폭 역시 잘 안되는데, 이게 드레인 전류 불안정 ,즉 모든

FET들이 saturation mode 에서 작동하지 않아서 output node에서 출력 swing이 이상한 것인지... 궁금합니다.

Q3) 그렇다면 이 문제들을 어떻게 해결해야할까요??

Q4) 소자 모델은 저것을 쓰는 것이 적합한 것인가요? ( neural opamp 설계 논문을 참조해서 쓴 모델인데, 더 적합한 모델 있다면 말씀해주시면 파라미터들은 찾아보겠습니다...)

댓글 3

pheonix님의 댓글

pheonix아무래도 낮아지는걸 보면 인풋 offset이 같이 낮아지는게 원인일듯 싶네요. 파라미터 설정이 맞나 확인해야하는데 아무래도 Hspice를 많이 다뤄본 선배나 조교한테 물어보는게 제일 빠를듯 싶습니다.

capstone님의 댓글

capstone

Hspice 툴 다루는 것 자체가 서툴렀던게 문제였네요. 교수님께 물어봐서 상당한 진척을 했습니다.

답변 고맙습니다^^

24FF님의 댓글

24FF발진하는 것 같은데, CC cap 과 M4 드레인 사이에 저항 하나 넣어보세요